Ethernet IC (10/100 [Mbps]) 個人的まとめ

今回は唐突に Ethernet IC についてまとめておこうと思います。

ここで扱う IC は特に新しいものでもないです。最近あたり前になっている 1000Mbps や 10Gbps の配線は難度が高く、気軽に手が出せません。 10/100 Mbps のものを対象としているためかいずれも発売から数年経ってます。書いており本人も特に詳しいわけでは無いです。

Ethernet IC の役割について

Ethernet IC とここで言っているものは

TCP/IP 4層モデルの最下層 または、OSI参照モデルの

物理層 データリンク層 を担うものです。

具体的な処理がイメージしづらいですが、

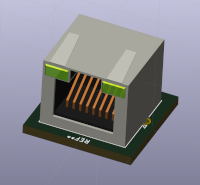

RJ-45 コネクタを介して流れる電気信号をビットとして読み書き、接続先とのリンクの確立、状態保持、エラー検知などを行うものです。

Ethernet 構成について

調査した Ethernet IC はいずれも 10/100Mbps 、1ポート対応のもの。10/100Mbps では 2.5MHz ~ 50MHz までのクロックを用いた信号を扱う。1Gbps になると 125MHz での動作が必要になる。

PHYとMACを接続するに MII(Media Independent Interface) と言われるプロトコルが使われる。MAC を PHY に依存しないようにして MII が規程されている。 これはデータ送受信に4線使用するので配線数が多くなる。1ポートで配線が 18本必要になる。この内 2本は各ポートと共有できるが、wikipedia に例があるとおりマルチポートになると信号線の数が問題になるようです。 例えば、MIIを使用する8ポートスイッチでは、8×16 + 2 = 130の信号が必要になる。

データ送受信を2線に抑えたもので RMII (Reduced Media Independent Interface) があり、こちらは1ポートに9本(内2本が共有線)となっている。MII と比較してデータ配線本数が少ない分クロックが高くなっており、50MHz での動作となる。

以降は RMII を前提として話を進めます。

RMII での 接続

データ線

- TX0

- TX1

- RX0

- RX1

管理用

- MDIO

- MDC

クロック

- REF_CLK

割り込み線

- EMAC_INT

キャリアセンス

- CRS_DV

計9本を PHY、MAC 間で接続する必要がある。

クロックについて

PHY、MACでの接続は配線以外にクロック源を必要とする。同期クロックを供給する方法として

- 25MHz クロックを PHY 層へ接続し、PHY 層から 50MHz として MAC 層へ伝播させる

- 50MHz クロックを PHY層と MAC層両方へ供給する

- 50MHz クロックを MAC 層から PHY 層へ伝播させる

が選択できる。 この選択における機能差や制限は特に記述がないようでしたが、基板のパターンを引くとき、パワープレーンの分離を考える時など少なからず影響するように思います。

ESP32 を使用する場合は ESP32 を MAC として 50MHz を出力することができるようなので部品数も増えなくて良さそうでした。

Ethernet IC 候補比較

候補となる IC は Digikey や JLCPCB で探してみました。いずれも 数ドルです。 以下に気になった点を列挙します。

- LAN8720A (2009 ~) https://www.microchip.com/wwwproducts/en/LAN8720A ~ $1 PHY IC industrial temperature range 対応あり 1.2V regulator 搭載 (on/off 可能) HP Auto-MDIX …

- W5500 (2013 ~ ) https://www.wiznet.io/product-item/w5500/ ~$2.5 MAC and PHY embedded SPI(~ 80MHz) interface for eacy integration WOL(Wake on LAN) & power down mode …

- DP83848C (2007 ~ ) https://www.ti.com/product/DP83848C ~$6 PHY IC industrial temperature range 対応あり Auto-MDIX JTAG … 他にもたくさんありますが、目についたものだけピックアップ。

まとめ

LAN8720 データシートを最初に読み始めたので基準となっているところがありますが、以下所感

- LAN8720 他のデータシートに目を通した後でも低電圧というところ以外は標準的 PHY なのかな? 安いので好印象。PHY、MAC 別体の一般的な構成。

- W5500 PHY & MAC 層両方をカバーしており SPI で制御できるところがユニーク。ソフトウェアエンジニアよりだととっつき安く感じるかも。しかし、PHY、MAC の詳細にふれず動作してしまいそうなので PHY、MAC を知る機会とならなそう。

- DP83848 JTAG対応なのでなにかあったときに内部を追いやすいのか?と。より過酷な状況下での動作保証に振っているような感じ。値段もその分高く、特に理由が無い限り使う必要がなさそう。

参考にしたサイト

TCP/IP 4層モデルや OSI参照モデルでの位置づけなどの説明

https://thinkit.co.jp/story/2015/04/30/5800

MII についての説明

https://www.macnica.co.jp/business/semiconductor/articles/microchip/134946/

こちらもMII についての説明。より詳細。

https://ja.wikipedia.org/wiki/Media-independent_interface

MAC をサポートする MCU のドキュメント。PHY との配線などの説明

https://docs.espressif.com/projects/esp-idf/en/latest/esp32/api-reference/network/esp_eth.html

JLCPCB 部品検索